Desain Cip Anyar Samsung & IBM Mendukung Baterai Ponsel Tahan hingga Seminggu

14 December 2021 |

13:21 WIB

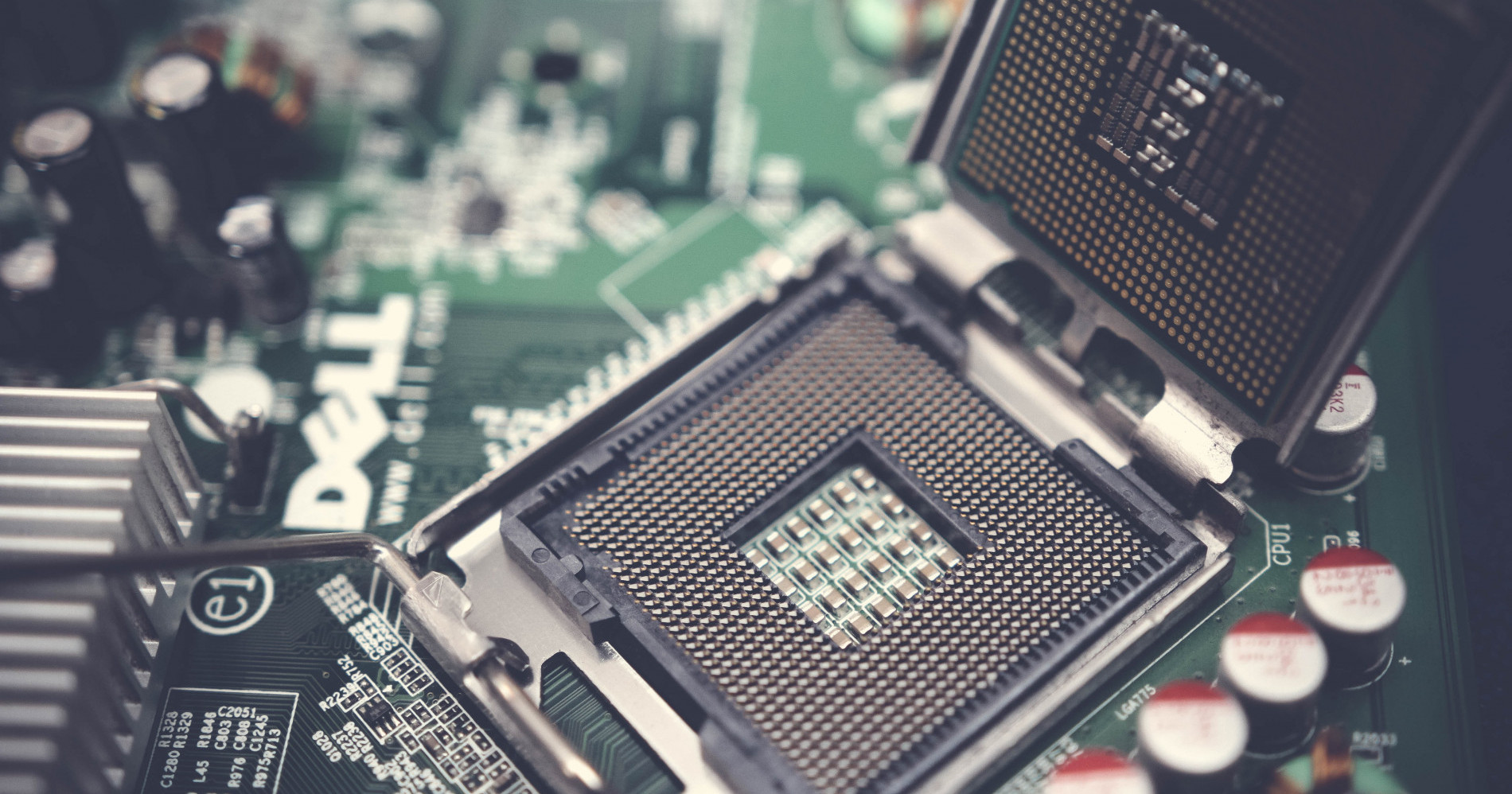

Raksasa teknologi asal Korea Selatan Samsung dan Amerika Serikat IBM, memperkenalkan model baru untuk susunan transistor dengan desain semikonduktor anyar yang dibuat menumpuk secara vertikal pada cipnya. Desain tersebut dapat mendukung performa baterai ponsel menjadi lebih efisien.

Melansir laporan Gizchina, arsitektur baru yang diperkenalkan menggunakan vertical transport field effect transistors (VTFET), sebuah transistor duduk tegak lurus satu sama lain dan arus mengalir melalui celah secara vertikal.

Sebagai informasi, dalam prosesor dan sistem cip yang ada saat ini, transistor terletak rata di permukaan. Jadi arus listrik mengalir dari sisi ke sisi. Adapun, transistor jenis baru memungkinkan kepadatan yang lebih besar dari komponen per cip dibandingkan yang ada saat ini.

Dengan demikian, ada potensi untuk meningkatkan efisiensi daya atau kinerja. Samsung dan IBM berupaya membuat efisiensi energi yang lebih sedikit untuk prosesnya tetapi menghasilkan kinerja yang juga lebih baik.

Kedua perusahaan mengatakan bahwa arsitektur baru ini akan menggandakan kinerja atau menggunakan daya 85 persen lebih sedikit ketimbang cip yang menggunakan transistor FinFET saat ini.

Menariknya, Samsung dan IBM membuat klaim yang berani mengenai manfaat dari teknologi ini. Menurut perusahaan, standar baru di masa depan memungkinkan smartphone digunakan selama seminggu penuh dalam sekali pengisian daya.

Perusahaan juga mengatakan bahwa arsitektur baru tersebut akan dapat dimanfaatkan untuk tugas-tugas intensif energi tertentu. Ini termasuk penambangan kripto yang lebih hemat daya, sehingga mendorong sisi positif terhadap lingkungan.

Sayangnya, kedua raksasa teknologi itu tidak mengungkap kapan desainnya akan mulai dikomersialkan. Kendati begitu, tampaknya inovasi ini masih akan membutuhkan banyak waktu untuk pengembangan lebih lanjut hingga dapat diimplementasikan.

Sebagai informasi, perusahaan bukan yang pertama memperkenalkan teknologi seperti ini. Intel juga tengah mengerjakan cip susun untuk menghemat energi yang dibutuhkan pada proses kinerja cip.

Tujuan Intel juga untuk membuat cip yang lebih hemat daya dan berkinerja lebih baik. Perusahaan memiliki visi untuk menyelesaikan desain cip pada 2024 dan akan muncul di node Intel 20A dan transistor RibbonFET perusahaan.

Editor: Fajar Sidik

Melansir laporan Gizchina, arsitektur baru yang diperkenalkan menggunakan vertical transport field effect transistors (VTFET), sebuah transistor duduk tegak lurus satu sama lain dan arus mengalir melalui celah secara vertikal.

Sebagai informasi, dalam prosesor dan sistem cip yang ada saat ini, transistor terletak rata di permukaan. Jadi arus listrik mengalir dari sisi ke sisi. Adapun, transistor jenis baru memungkinkan kepadatan yang lebih besar dari komponen per cip dibandingkan yang ada saat ini.

Dengan demikian, ada potensi untuk meningkatkan efisiensi daya atau kinerja. Samsung dan IBM berupaya membuat efisiensi energi yang lebih sedikit untuk prosesnya tetapi menghasilkan kinerja yang juga lebih baik.

Kedua perusahaan mengatakan bahwa arsitektur baru ini akan menggandakan kinerja atau menggunakan daya 85 persen lebih sedikit ketimbang cip yang menggunakan transistor FinFET saat ini.

Menariknya, Samsung dan IBM membuat klaim yang berani mengenai manfaat dari teknologi ini. Menurut perusahaan, standar baru di masa depan memungkinkan smartphone digunakan selama seminggu penuh dalam sekali pengisian daya.

Perusahaan juga mengatakan bahwa arsitektur baru tersebut akan dapat dimanfaatkan untuk tugas-tugas intensif energi tertentu. Ini termasuk penambangan kripto yang lebih hemat daya, sehingga mendorong sisi positif terhadap lingkungan.

Sayangnya, kedua raksasa teknologi itu tidak mengungkap kapan desainnya akan mulai dikomersialkan. Kendati begitu, tampaknya inovasi ini masih akan membutuhkan banyak waktu untuk pengembangan lebih lanjut hingga dapat diimplementasikan.

Sebagai informasi, perusahaan bukan yang pertama memperkenalkan teknologi seperti ini. Intel juga tengah mengerjakan cip susun untuk menghemat energi yang dibutuhkan pada proses kinerja cip.

Tujuan Intel juga untuk membuat cip yang lebih hemat daya dan berkinerja lebih baik. Perusahaan memiliki visi untuk menyelesaikan desain cip pada 2024 dan akan muncul di node Intel 20A dan transistor RibbonFET perusahaan.

Editor: Fajar Sidik

Komentar

Silahkan Login terlebih dahulu untuk meninggalkan komentar.